- 您现在的位置:买卖IC网 > Sheet目录3886 > PIC16F1827-I/ML (Microchip Technology)IC PIC MCU FLASH 4K 28-QFN

SC16C850

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2010. All rights reserved.

Product data sheet

Rev. 2 — 11 November 2010

37 of 55

NXP Semiconductors

SC16C850

2.5 to 3.3 V UART with 128-byte FIFOs and IrDA encoder/decoder

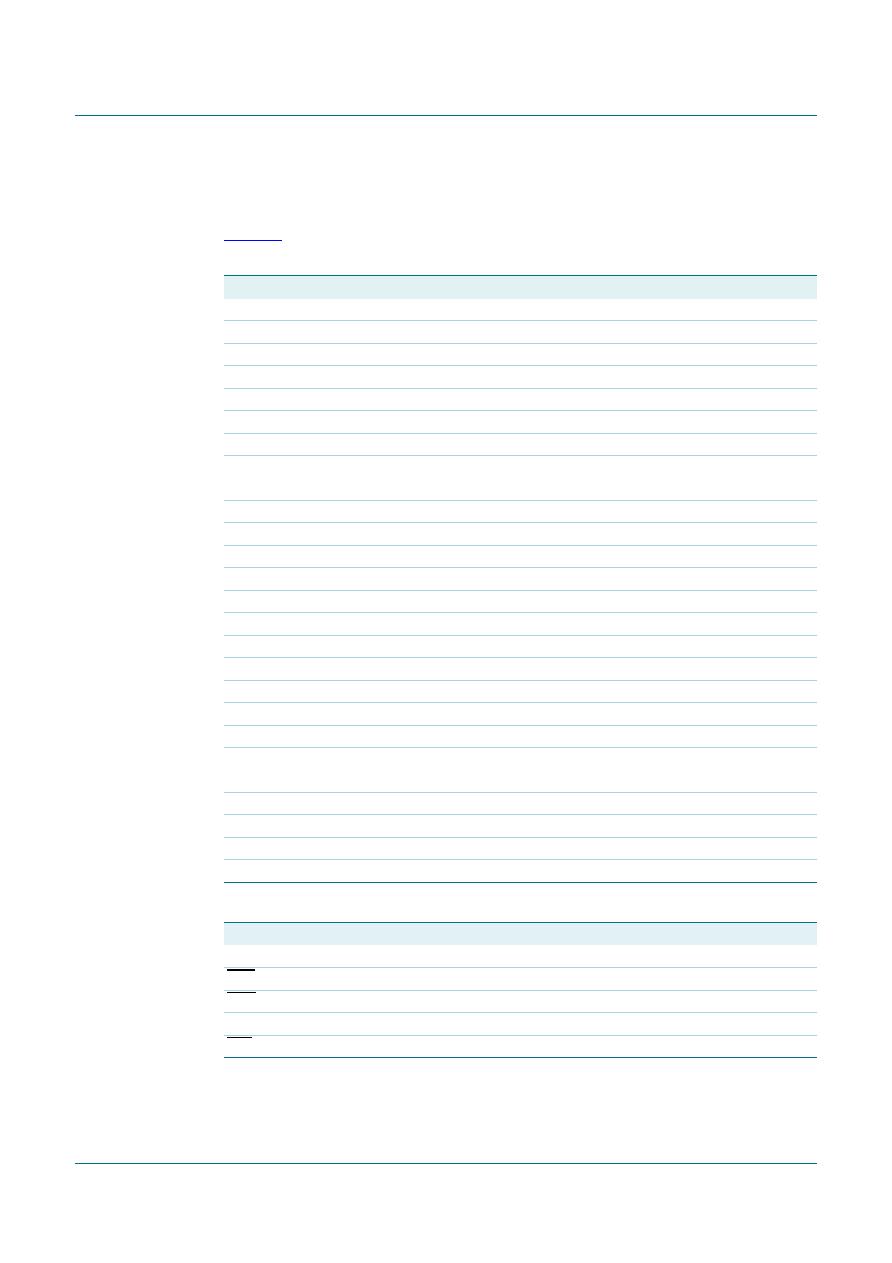

7.23 SC16C850 external reset condition and software reset

These two reset methods are identical and will reset the internal registers as indicated in

Table 33.

Reset state for registers

Register

Reset state

IER

IER[7:0] = 0

FCR

FCR[7:0] = 0

ISR

ISR[7:1] = 0; ISR[0] = 1

LCR

LCR[7:0] = 0

MCR

MCR[7:0] = 0

LSR

LSR[7] = 0; LSR[6:5] = 1; LSR[4:0] = 0

MSR

MSR[7:4] = input signals; MSR[3:0] = 0

EFCR

EFCR[7:0] = 0

SPR

SPR[7:0] = 1

DLL

undefined

DLM

undefined

TXLVLCNT

TXLVLCNT[7:0] = 0

RXLVLCNT

RXLVLCNT[7:0] = 0

EFR

EFR[7:0] = 0

Xon1

undefined

Xon2

undefined

Xoff1

undefined

Xoff2

undefined

TXINTLVL

TXINTLVL[7:0] = 0

RXINTLVL

RXINTLVL[7:0] = 0

FLWCNTH

FLWCNTH[7:0] = 0

FLWCNTL

FLWCNTL[7:0] = 0

CLKPRES

CLKPRES[7:0] = 0

RS485TIME

RS485TIME[7:0] = 0

AFCR2

AFCR2[7:0] = 0

AFCR1

AFCR1[7:0] = 0

Table 34.

Reset state for outputs

Output

Reset state

TX

logic 1

RTS

logic 1

DTR

logic 1

INT

logic 0

IRQ

open-drain

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16LCE624T-04E/SO

IC MCU CMOS 1K OTP W/EEPRM18SOIC

PIC16LF1827-I/ML

IC PIC MCU FLASH 4K 28-QFN

PIC16LCE624-04E/SS

IC MCU CMOS 1K OTP W/EEPRM20SSOP

PIC16F687-I/P

IC PIC MCU FLASH 2KX14 20DIP

PIC16LF1829-I/SO

MCU PIC 14KB FLASH 20-SOIC

PIC16LCE624-04E/SO

IC MCU CMOS 1K OTP W/EEPRM18SOIC

PIC16F1829-I/SO

MCU PIC 14K FLASH 1K RAM 20SOIC

PIC16F685-I/SS

IC PIC MCU FLASH 4KX14 20SSOP

相关代理商/技术参数

PIC16F1827-I/MQ

功能描述:8位微控制器 -MCU 7KB Flash 384 byte 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1827-I/MV

功能描述:8位微控制器 -MCU 7KB Flash 384 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1827-I/P

功能描述:8位微控制器 -MCU 7KB Flash 384 byte 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1827-I/SO

功能描述:8位微控制器 -MCU 7KB Flash 384 byte 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1827-I/SS

功能描述:8位微控制器 -MCU 7KB Flash 384 byte 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1827T-I/ML

功能描述:8位微控制器 -MCU 7KB Flash 384 byte 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1827T-I/MQ

功能描述:8位微控制器 -MCU 7KB Flash 384 byte 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1827T-I/MV

功能描述:8位微控制器 -MCU 7KB Flash 384 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT